|

|

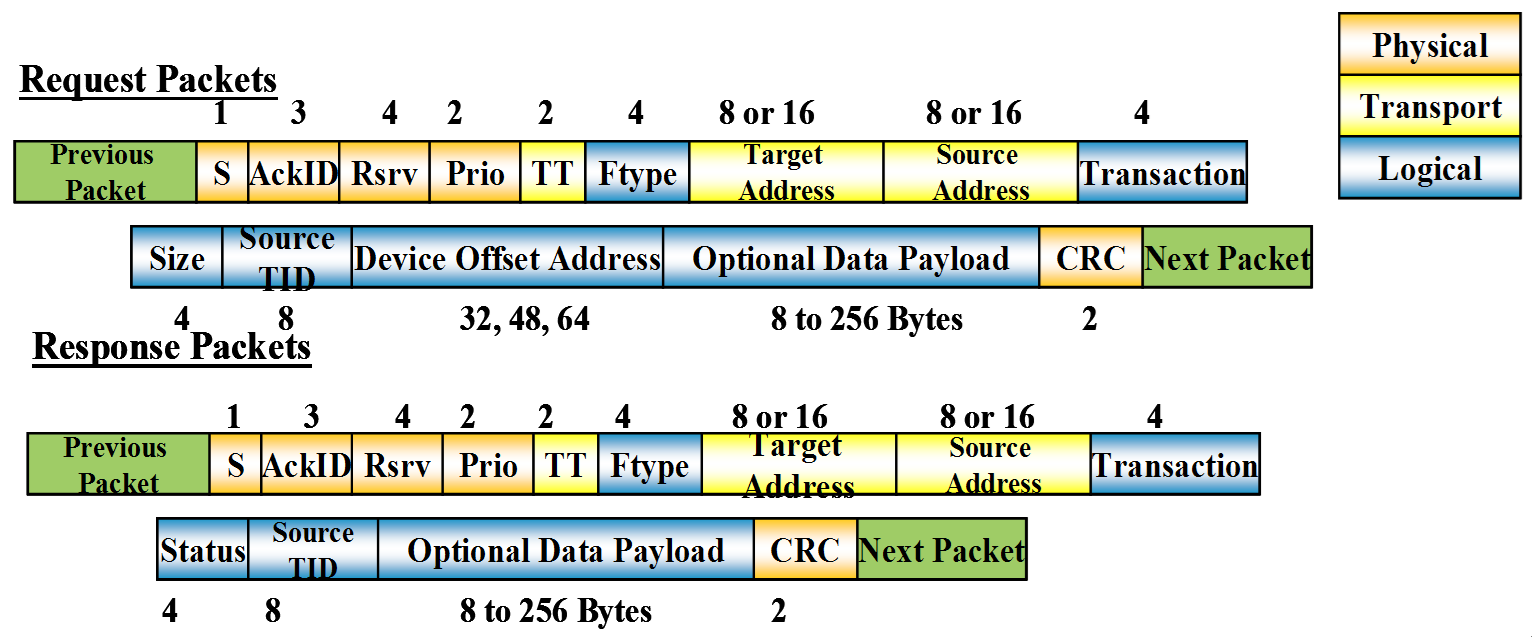

RapidIO包由代表3级规范体系结构的多个字段组成。下图显示了典型的请求包和响应包的格式,这些包的格式属于并行物理层包格式,串行物理层包的格式与此稍有不同。某些字段是依赖于具体的上下文的, 并不会在所有的包中出现。

请求包以物理层字段开始, S位指示这是一个包还是一个控制符号(S=0表示是一个包,S=1表示是控制符号), AckID表明交换结构器件将用控制符号来确认哪一个包。PRIO字段指示用于流量控制的包优先级。TT、目标地址( Target Address)和源地址( Source Address)字段指示传输地址的机制类型、包应被传送到的器件的地址和产生包的器件的地址。Ftype和事务(Transation)指示正被请求的事务。长度(Size)字段等于编码后事务的长度, RapidIO事务数据的有效裁荷(Payload)长度从1到256字节不等。SrcTID(源事务ID)指示事务ID, RapidIO器件在两个端点器件间最多允许有256个未完成的事务。对于存储器映射事务,跟随在srcTID后面的是器件偏移地址 (Device Offset Address ) 字段。写事务必须附带数据的有效裁荷,所有包以16位(2个字节)循环冗余校验码(CRC)结束。

响应包与请求包类似。状态(Status)字段指示是否成功完成了事务。目标TID(目标事务ID)字段的值与请求包中源事务 ID字段的值相等。下图是请求包与响应包的包格式示意图

对于用户来说,最需要关注的就是逻辑层(上图中蓝色部分)各个字段的含义,逻辑层中Ftype与Ttype(Ttype字段和上图中的Transaction字段是同一个字段,只不过叫法不同而已)两个字段唯一的确定了这个请求包的功能。下表列出了Ftype与Ttype所确定的包含义

Ftype

(Format Type)

Ttype

(Transaction Type)

包类型

功能

0~1

——

Reserve

无

2

4’b0100

NREAD

读指定的地址

4’b1100

ATOMIC increment

先往指定的地址中传递数据,在把传递的数据加1,此操作为原子操作,不可打断

4’b1101

ATOMIC decrement

先往指定的地址中传递数据,在把传递的数据减1,此操作为原子操作,不可打断

4’b1110

ATOMIC set

把指定地址中的数据每个bit全部写1

4’b1111

ATOMIC clear

把指定地址中的数据清0(每个bit全部清零)

3~4

——

Reserve

无

5

4’b0100

NWRITE

往指定的地址写数据

4’b0101

NWRITE_R

往指定的地址写数据,写完成以后接收目标器件(Target)的响应

4’b1101

ATOMIC test/swap

对指定地址中的数据进行测试并交换,此操作为原子操作,不可打断

6

4’bxxxx

SWRITE

以流写方式写指定的地址,与NWRITE以及NWRITE_R相比,此方式效率最高

7

——

Reserve

无

8

4’b0000

MAINTENANCE read request

发起读配置,控制,状态寄存器请求

4’b0001

MAINTENANCE write request

发起写配置,控制,状态寄存器请求

4’b0010

MAINTENANCE read response

产生读配置,控制,状态寄存器响应

4’b0011

MAINTENANCE write response

产生写配置,控制,状态寄存器响应

4’b0100

MAINTENANCE write resquest

端口写请求

9

——

Reserve

无

10

4’bxxxx

DOORBELL

门铃

11

4’bxxxx

MESSAGE

消息

12

——

Reserve

无

13

4’b0000

RESPONSE

no data

不带有效数据的响应包

4’b1000

RESPONSE

with data

带有效数据的响应包

14~15

——

Reserve

无

|

|

/1

/1

|小黑屋|手机版|Archiver|fpga论坛|fpga设计论坛

( 京ICP备20003123号-1 )

|小黑屋|手机版|Archiver|fpga论坛|fpga设计论坛

( 京ICP备20003123号-1 )