|

|

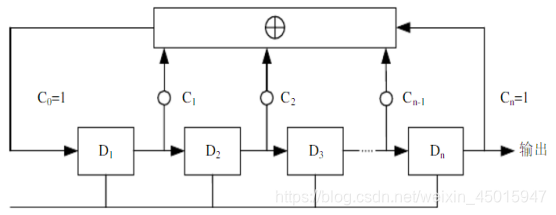

图(1)示出的是由n级移位寄存器构成的码序列发生器。寄存器的状态决定于时钟控制下输入的信息(“0”或“1”),例如第I级移位寄存器状态决定于前一时钟脉冲后的第i-1级移位寄存器的状态。

图中C0,C1,…,Cn均为反馈线,其中C0=C1=1,表示反馈连接。因为m序列是由循环序列发生器产生的,因此C0和Cn肯定为1,即参与反馈。而反馈系数C1,C2,…,Cn-1,若为1,参与反馈;若为0,则表示断开反馈线,即开路,无反馈连线。

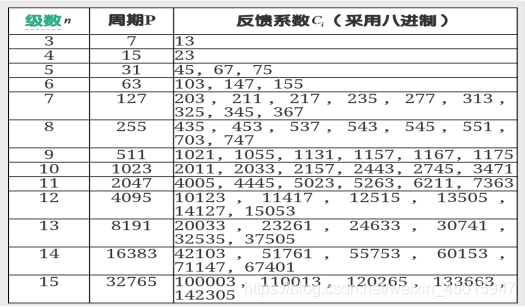

一个线性反馈移动寄存器能否产生m序列,决定于它的反馈系数Ci ( i=0,1,2,…n) ,下表中列出了部分m序列的反馈系数 ,按照下表中的系数来构造移位寄存器,就能产生相应的m序列。

根据表1中的八进制的反馈系数,可以确定m序列发生器的结构。以7级m序列反馈系数Ci=(211)8为例,首先将八进制的系数转化为二进制的系数即Ci=(010001001)2,由此我们可以得到各级反馈系数分别为:C0=1,C1=0,C2=0,C3=0,C4=1,C5=0,C6=0,C7=1,由此就很容易地构造出相应的m序列发生器。根据反馈系数,其他级数的m序列的构造原理与上述方法相同。 |

|

/1

/1

|小黑屋|手机版|Archiver|fpga论坛|fpga设计论坛

( 京ICP备20003123号-1 )

|小黑屋|手机版|Archiver|fpga论坛|fpga设计论坛

( 京ICP备20003123号-1 )